# SV3C CPTX MIPI C-PHY Generator

#### Ordering Information:

800 Village Walk #316 Guilford, CT 06437 Ph: 203-401-8093

Email orders to: <a href="mailto:sales@xsoptix.com">sales@xsoptix.com</a>

Fax orders to: 800-878-7282

**Data Sheet**

## Table of Contents

| Table of Contents                                        | 1        |

|----------------------------------------------------------|----------|

| List of Figures                                          |          |

| List of Tables                                           |          |

| Introduction                                             |          |

| Overview                                                 |          |

| Key Benefits                                             |          |

| Applications                                             |          |

| Features                                                 |          |

| Overall Block Diagram and Signal Generation Concepts     | 4        |

| Burst-Mode Pattern Definition and Generation             |          |

| Global Timing Parameter Controls                         | 7        |

| Manipulating Non-Payload Data Portions of a Transmission | 8        |

| Analog Parameter Controls                                | <u>c</u> |

| Automation                                               | 12       |

| Physical Description and Pinout                          | 13       |

| Specifications                                           |          |

|                                                          |          |

# List of Figures

| Figure 1   | High-level block diagram of SV3C CPTX 4-Lane C-PHY Generator.                               | 1 |

|------------|---------------------------------------------------------------------------------------------|---|

| Figure 2   | Global waveform showing LP and HS C-PHY transmissions on one lane (3 wires)                 | 5 |

| Figure 3   | Basic concept of packet transmission.                                                       | 5 |

| Figure 4   | Distinction between Test Pattern length and packet size when transmitting fixed patterns in |   |

| burst mod  | de6                                                                                         | õ |

| Figure 5   | Data definition method within the IntrospectESP software                                    | õ |

| Figure 6   | Global timing parameter control from within the cphyPattern component                       | 7 |

| Figure 7   | Toggling 'hsDataMode' to symbol automatically converts the packet payload data into C-PHY   |   |

| symbol re  | presentation                                                                                | 3 |

| Figure 8   | cphyPattern component showing how to manipulate non-payload portions of a transmission.8    | 3 |

| Figure 9   | Description of non-payload data and timings                                                 | ) |

| Figure 10  | Description of non-payload data and timings                                                 | ) |

| Figure 11  | (a) Single-ended waveform out of generator, and (b) differential signal seen by a C-PHY     |   |

| receiver c | onnected to two wires out of the generator10                                                | ) |

| Figure 12  | Illustration of HS common-mode signal control. Negative and positive voltages are produced  |   |

|            | 10                                                                                          | ) |

| Figure 13  | Illustration of LP signal level control. Negative and positive voltages are produced        | L |

| Figure 14  | Differential AB and BC in which one of the eyes is closed with DCD injection13              | L |

| Figure 15  | Screen captures of the IntrospectESP user environment                                       | 2 |

| Figure 16  | Illustration of the SV3C CPTX C-PHY Generator connectors                                    | 3 |

|            |                                                                                             |   |

## List of Tables

| Table 1 | Physical Dimensions                              | 13 |

|---------|--------------------------------------------------|----|

|         | Listing of SV3C-CPTX connectors                  |    |

| Table 3 | Mapping of Lower MXP Connector (Lane Pinout)     | 14 |

| Table 4 | Mapping of Upper MXP Connector (Replica Signals) | 14 |

| Table 5 | General Specifications                           | 15 |

| Table 6 | Transmitter Characteristics                      | 16 |

| Table 7 | Clocking Characteristics                         | 17 |

| Table 8 | Pattern Handling Characteristics                 | 17 |

#### Introduction

#### **Overview**

The SV3C-CPTX C-PHY Generator is an ultra-portable, high-performance instrument that enables exercising and validating MIPI C-PHY receiver ports. Capable of generating any traffic and being completely data-rate agile, the C-PHY generator includes analog parameter controls that enable gaining deep insights into receiver sensitivity performance and skew/jitter tolerance.

The C-PHY Generator operates using the highly versatile IntrospectESP Software environment. This environment allows for automating receiver tests such as voltage sensitivity or wire-skew tolerance. The environment also includes MIPI pattern compiler tools that enable the generation of complete DSI or CSI packets such as those characteristic of color bars or active image frames.

This document describes the electrical characteristics and key specifications of the C-PHY Generator. Please refer to IntrospectESP software documentation for additional operating instructions.

#### **Key Benefits**

- Any-rate operation and global timing parameter control

- Per-wire skew injection with < 1 ps resolution

- Per-wire voltage level control

- Per-wire LP generation

- State of the art programming environment based on the highly intuitive Python language

- Reconfigurable, protocol customization (on request)

#### **Applications**

- Parallel physical layer validation

- Interface test

- Plug-and-play system-level validation

#### **Features**

#### **Overall Block Diagram and Signal Generation Concepts**

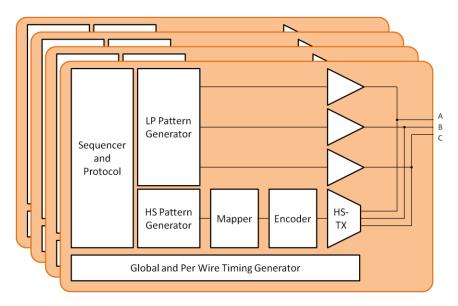

The SV3C CPTX is a pattern generator capable of creating both LP and HS data streams across four C-PHY lanes simultaneously. Illustrated in Figure 1, the pattern generator architecture offers individual control over LP events, HS events, and global timing events on a per-wire basis. Thus, it provides complete electrical test coverage in a manner similar to AWG solutions while still being versatile enough to generate compliant CSI-2 packets and video frames from within a seamless software environment.

Built into the HS generators within the SV3C CPTX are dedicated hardware C-PHY mapper and encoder circuits as shown in Figure 1. This allows for tremendous ease of use as will be described in later sections of this document. Specifically, when defining packet transmissions, the user need not construct wire states or transitions manually (unless he/she so desires) and can just define 16-bit integer payload data.

Figure 1 High-level block diagram of SV3C CPTX 4-Lane C-PHY Generator.

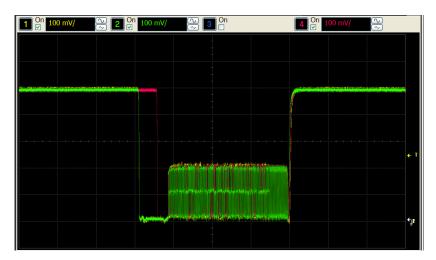

Figure 2 Global waveform showing LP and HS C-PHY transmissions on one lane (3 wires).

Figure 2 shows a packet transmission using the C-PHY generator. As can be seen, the packet starts from the STOP state, enters into HS mode, and then transmits three-phase encoded data on the three wires. In the next section, we will describe how one can define such packet transmissions both from a payload perspective and a timing/voltage stress perspective.

#### **Burst-Mode Pattern Definition and Generation**

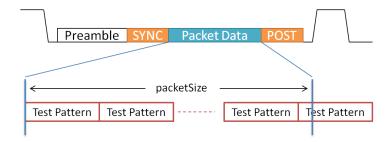

In its most typical use case, the SV3C CPTX generator is programmed to generate payload data as shown in Figure 3. The payload data is highlighted in the figure, and it can consist of fixed Test Patterns (e.g. PRBS data) or active packets as part of a video frame.

When it comes to Test Pattern transmission, Figure 4 illustrates how packet length is not necessarily constrained to be equal to Test Pattern size in the SV3C CPTX generator. In fact, packet size can be much larger than Test Pattern length. For example, the Test Pattern can be a very short 16-bit or 32-bit sequence, and the packet size can be much larger. In this case, the Test Pattern is assumed to repeat continuously within a packet as shown in Figure 4.

Figure 3 Basic concept of packet transmission.

Figure 4 Distinction between Test Pattern length and packet size when transmitting fixed patterns in burst mode.

Defining the HS pattern to be transmitted is performed using the cphyPattern component within the IntrospectESP software as shown in Figure 5. Using this component, one is able to define the payload data within a transmission using high-level software commands. For example, shown in the figure is an array of 8 different 16-bit integer values representing counts from 1 to 8 and defined in the 'hsData' parameter of the cphyPattern component. When declared in this manner, the packet transmission in Figure 3 would play the 8 integer values within the active portion of the packet after automatic three-phase mapping and encoding in hardware.

In order to generate PRBS payload data within a packet, the 'hsDataMode' parameter of the cphyPattern component can be set to PRBS and the appropriate polynomial order and seed values can be selected.

| Components  | cphyPattem1 properties (class: MipiCphyPatte |                          |

|-------------|----------------------------------------------|--------------------------|

| cphyPattem1 | pattemType                                   | packetLoop               |

|             | hsDataMode                                   | integer                  |

|             | hsPrbsOrder                                  |                          |

|             | hsPrbsSeed                                   |                          |

|             | hsData                                       | [1, 2, 3, 4, 5, 6, 7, 8] |

|             | hsSymbols                                    |                          |

|             | packet Size                                  | 1000                     |

|             | split Data Across Lanes                      | False                    |

|             | sameDataInEachPacket                         | True                     |

Figure 5 Data definition method within the IntrospectESP software.

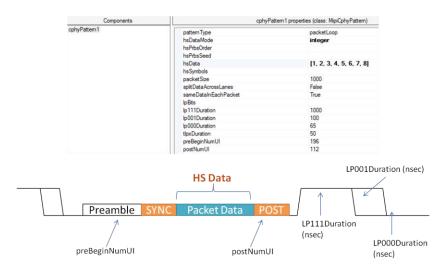

#### **Global Timing Parameter Controls**

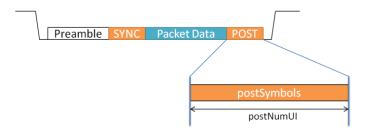

Similar to payload data definition, the SV3C CPTX allows for controlling global timing parameters, and this is useful for automatically verifying HS receiver functionality under varying timing conditions. Figure 6 shows the cphyPattern component again with additional parameters related to packet timings. As can be seen, parameters such as preBeginNumUI and postNumUI allow for varying the timings associated with starting HS transmissions and ending them. Similarly, parameters such as Ip000Duration allow for varying the preparation (termination enable) period when testing receivers in burst mode.

Figure 6 Global timing parameter control from within the cphyPattern component.

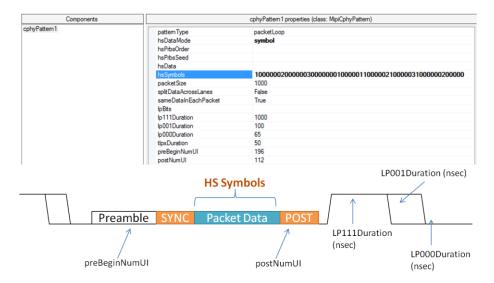

It is interesting at this stage to highlight another pattern generation feature of the SV3C CPTX. It was mentioned in the previous section that payload data can be entered in integer format. However, if there is a need to define data in symbol format, or – better yet – to quickly verify what an integer value corresponds to in C-PHY symbol format, then the Introspect ESP software can be used to automatically switch between the two number representations. Referring to Figure 7, the same 8 integer values that were declared in the 'hsData' parameter of Figure 5 are now displayed in C-PHY symbol format. This was achieved by simply toggling the 'hsDataMode' from 'integer' to 'symbol'. Note that each integer now maps to 7 symbols as per the C-PHY mapping technology.

Figure 7 Toggling 'hsDataMode' to symbol automatically converts the packet payload data into C-PHY symbol representation.

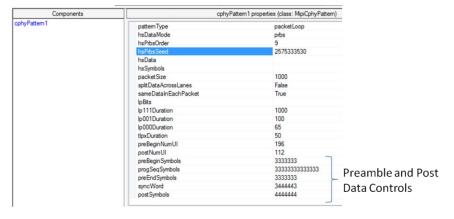

#### **Manipulating Non-Payload Data Portions of a Transmission**

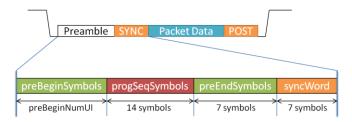

In previous sections, we described how to manipulate payload data and global timing parameters of packet transmissions. What remains is to manipulate non-payload portions of a transmission. Namely, the SV3C CPTX generator allows for sending invalid preamble data, sync word data, and post data. These are all additional parameters in the cphyPattern component as shown in Figure 8. Figure 9 and Figure 10 show how the timing parameters apply to these non-payload data transmissions.

Figure 8 cphyPattern component showing how to manipulate non-payload portions of a transmission.

Figure 9 Description of non-payload data and timings.

Figure 10 Description of non-payload data and timings.

#### **Analog Parameter Controls**

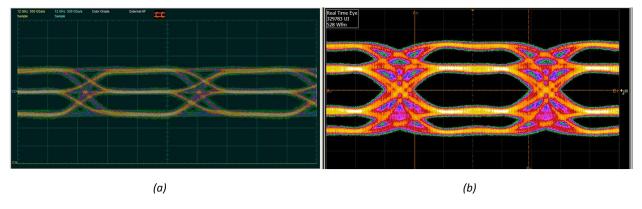

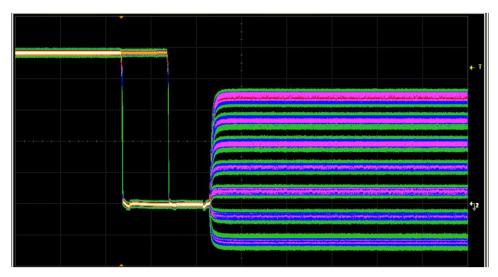

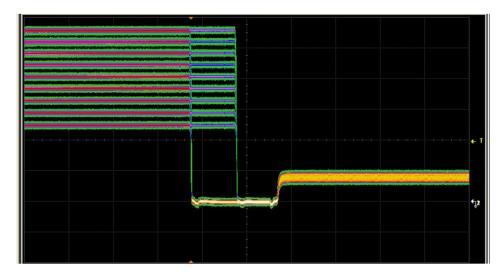

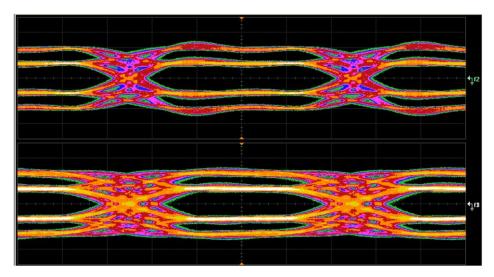

As required by the C-PHY standard, each wire out of the SV3C CPTX generator produces three-level single ended waveforms as shown in Figure 11(a). The span of the waveform (i.e. distance from the low level to the high level) is defined as single-ended voltage swing in this document, and it corresponds to the VOD specification in the C-PHY standard. Additionally, in order to enable receiver stressed eye testing, the generator includes common-mode control in which the entire waveform (low, mid, and high levels) is shifted up or down based on software commands (Figure 12). Similarly, all LP levels are programmable with fine resolution as shown in Figure 13. Such programmability is necessary for enabling various tests related to LP/HS interactions in C-PHY. Finally, advanced options exist for manipulating symmetry of the wire HS voltages (mid-level control), and these are all intended to help close the differential eye seen by a receiver (Figure 11 (b)).

Figure 11 (a) Single-ended waveform out of generator, and (b) differential signal seen by a C-PHY receiver connected to two wires out of the generator.

Figure 12 Illustration of HS common-mode signal control. Negative and positive voltages are produced.

Figure 13 Illustration of LP signal level control. Negative and positive voltages are produced.

Coming back to receiver stressed eye testing, key to the SV3C CPTX Generator functionality is the ability to perturb timings on the wires within a C-PHY lane individually. This allows for receiver stress signal calibration or for receiver stress testing. Figure 14 shows an example of the AB and BC differential eyes in which DCD is injected on one of the pairs. As can be seen, high precision eye closure (fraction of the symbol interval) is achieved and can be used to gradually stress a receiver until failure is observed. The SV3C CPTX is able to create skew with a resolution of 1 ps or less and a range of about +/- 1 UI.

Figure 14 Differential AB and BC in which one of the eyes is closed with DCD injection.

#### **Automation**

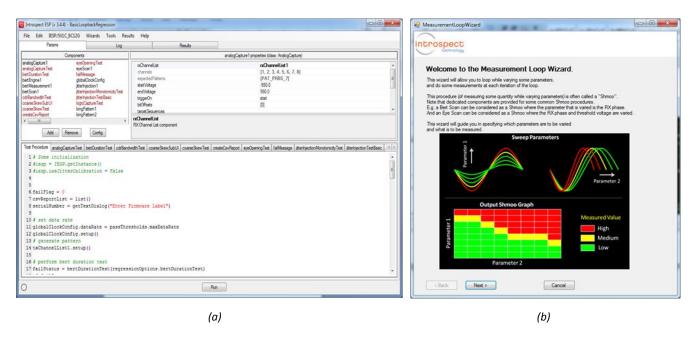

The SV3C CPTX C-PHY Generator is operated using the award winning IntrospectESP Software. It features a comprehensive scripting language with an intuitive component-based design as shown in the screen shot in Figure 15(a). Component-based design is IntrospectESP's way of organizing the flexibility of the instrument in a manner that allows for easy program development. It highlights to the user only the parameters that are needed for any given task, thus allowing program execution in a matter of minutes. For further help, the software environment features automatic code generation for common tasks such as Measurement Loop generation as shown in Figure 15(b).

Figure 15 Screen captures of the IntrospectESP user environment.

### Physical Description and Pinout

Figure 16 shows a diagram of the physical ports of the SV3C CPTX and Table 1 provides the physical dimensions for the unit. More detailed information on the SV3C-CPTX connectors and pinout is provided in Table 2.

Figure 16 Illustration of the SV3C CPTX C-PHY Generator connectors.

Table 1 Physical Dimensions

| Parameter | Value             |

|-----------|-------------------|

| Length    | 9.5" (241.3 mm)   |

| Width     | 4.25" (107.95 mm) |

| Height    | 1.3" (33.3 mm)    |

| Weight    | 2 lb              |

Table 2 Listing of SV3C-CPTX connectors

| Port / Indicator Name    | Connector Type        |

|--------------------------|-----------------------|

| Ref Clock In             | SMP Differential Pair |

| Ref Clock Out A          | SMP Differential Pair |

| Ref Clock Out B          | SMP Differential Pair |

| TX Lane 1 – 4            | MXP (Lower Connector) |

| Replica Signals          | MXP (Upper Connector) |

| USB Port                 | USB                   |

| Power Switch / Connector | _                     |

The lower MXP connector, as shown in Figure 16, provides the TX Lane 1-4 output signals. The pin mapping for this lower connector is provided in Table 3 below.

The upper MXP connector provides four replica signals which may be connected directly to an external measurement device for live monitoring. The pin mapping for this upper connector is provided in Table 4 below.

Table 3 Mapping of Lower MXP Connector (Lane Pinout)

| 1 9                  | <b>Connector Pin Number</b> | Corresponding TX Lane |

|----------------------|-----------------------------|-----------------------|

| 2 10<br>3 11         | 1,2,3                       | Lane 1 (A,B,C)        |

| 4 12<br>5 13         | 9,10,11                     | Lane 2 (A,B,C)        |

| 6 14<br>7 15<br>8 16 | 4,5,6                       | Lane 3 (A,B,C)        |

| 8 16                 | 12,13,14                    | Lane 4 (A,B,C)        |

Table 4 Mapping of Upper MXP Connector (Replica Signals)

|                     | Connector Pin Number | Corresponding TX Lane |

|---------------------|----------------------|-----------------------|

| 1 9<br>2 10<br>3 11 | 7                    | Lane 1 (A)            |

| 4 12<br>5 13        | 8                    | Lane 3 (A)            |

| 6 14<br>7 15        | 15                   | Lane 2 (A)            |

| 8 16                | 16                   | Lane 4 (A)            |

# Specifications

| Table 5 General Specifications Parameter  | Value                    | Units | Description and Conditions                                                                                                 |

|-------------------------------------------|--------------------------|-------|----------------------------------------------------------------------------------------------------------------------------|

|                                           | value                    | Units | Description and Conditions                                                                                                 |

| Application / Protocol Support            |                          |       |                                                                                                                            |

| Physical layer interface                  | C-PHY                    |       |                                                                                                                            |

| MIPI protocol                             | CSI/DSI                  |       | Flexible pattern architecture allows for the generation of encoded PHY data or entire CSI/DSI frames                       |

| LP/HS Handling                            | Automatic                |       | Tester automatically generates LP and HS data                                                                              |

| Ports                                     |                          |       |                                                                                                                            |

| Number of Transmitter Lanes               | 4                        |       |                                                                                                                            |

| Number of Dedicated Clock Outputs         | 2                        |       | Separate clock for providing reference to the DUT                                                                          |

| Number of Dedicated Clock Inputs          | 1                        |       | Used as external Reference Clock input                                                                                     |

| Number of Trigger Input Pins              | 3                        |       | Armed in software to trigger the start of specific measurements                                                            |

| Number of Flag Output Pins                | 3                        |       | Armed in software to flag test completion or pass/fail criteria                                                            |

| Data Rates and Frequencies                |                          |       |                                                                                                                            |

| Minimum Data Rate                         | 80                       | Msps  |                                                                                                                            |

| Maximum Data Rate                         | 3.0                      | Gsps  |                                                                                                                            |

| Minimum External Input Clock<br>Frequency | 10                       | MHz   |                                                                                                                            |

| Maximum External Input Clock<br>Frequency | 250                      | MHz   |                                                                                                                            |

| Minimum LP State Period                   | 43                       | ns    | LP period resolution is based on programmed HS data rate. Compiler automatically selects period to satisfy user selection. |

| Maximum LP State Period                   | Software<br>Programmable | ns    |                                                                                                                            |

Table 6 Transmitter Characteristics

| Table 6 Transmitter Characteristics  Parameter           | Value                                                        | Units | Description and Conditions                                                                                                                                                    |

|----------------------------------------------------------|--------------------------------------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HS Output Coupling                                       |                                                              |       | Pro                                                                                                                                       |

| Output Single-Ended Impedance                            | 50                                                           | Ω     |                                                                                                                                                                               |

| Output Impedance Tolerance                               | +/-5                                                         | Ω     |                                                                                                                                                                               |

| HS Voltage Performance                                   |                                                              |       |                                                                                                                                                                               |

| Minimum Single-Ended Output<br>Voltage Swing             | 0                                                            | mV    |                                                                                                                                                                               |

| Maximum Single-Ended Output Voltage Swing                | 400                                                          | mV    |                                                                                                                                                                               |

| Voltage Resolution                                       | 10                                                           | mV    |                                                                                                                                                                               |

| Accuracy of Voltage Programming                          | larger of: +/-1.5%<br>of programmed<br>value, and +/-<br>5mV | %, mV |                                                                                                                                                                               |

| Rise and Fall Time                                       | 90*                                                          | ps    | * Optimized for C-PHY receiver testing                                                                                                                                        |

| Level Setting                                            | Per-Wire                                                     |       |                                                                                                                                                                               |

| Per Wire HS Jitter Performance                           |                                                              |       |                                                                                                                                                                               |

| Random Jitter Noise Floor                                | 1.5                                                          | ps    | Based on measurement with a high-bandwidth real-<br>time scope and with first-order clock recovery                                                                            |

| Minimum Frequency of Injected<br>Deterministic Jitter    | 0.1                                                          | kHz   |                                                                                                                                                                               |

| Maximum Frequency of Injected<br>Deterministic Jitter    | 80                                                           | MHz   |                                                                                                                                                                               |

| Frequency Resolution of Injected<br>Deterministic Jitter | 0.1                                                          | kHz   |                                                                                                                                                                               |

| Maximum Peak-to-Peak Injected<br>Deterministic Jitter    | 2                                                            | UI    |                                                                                                                                                                               |

| Magnitude Resolution of Injected<br>Deterministic Jitter | 500                                                          | fs    | Jitter injection is based on multi-resolution synthesizer, so this number is an effective resolution. Internal synthesizer resolution is defined in equivalent number of bits |

| Accuracy of Injected Jitter<br>Magnitude                 | larger of: +/-2% of<br>programmed<br>value, and +/-2 ps      | %, ps |                                                                                                                                                                               |

| HS Lane-to-Lane Skew Performance                         |                                                              |       |                                                                                                                                                                               |

| Lane to Lane Integer-UI Minimum<br>Skew                  | -20                                                          | UI    |                                                                                                                                                                               |

| Lane to Lane Integer-UI Maximum<br>Skew                  | 20                                                           | UI    |                                                                                                                                                                               |

| Effect of Skew Adjustment on Jitter Injection            | None                                                         |       |                                                                                                                                                                               |

| HS Intra-Lane Wire-to-Wire Skew Performance*             |                                                              |       | * Limitations in range exist at low data rates                                                                                                                                |

| Minimum Wire to Wire Skew                                | -1                                                           | UI    |                                                                                                                                                                               |

| Maximum Wire to Wire Skew                                | 1                                                            | UI    |                                                                                                                                                                               |

| Skew Injection Resolution                                | 1                                                            | ps    |                                                                                                                                                                               |

| LP Voltage Controls                      |                  |    |                                      |

|------------------------------------------|------------------|----|--------------------------------------|

| Minimum Programmable Logic High<br>Level | 600              | mV |                                      |

| Maximum Programmable Logic<br>High Level | 2000             | mV | * Extended range under investigation |

| Minimum Programmable Logic Low<br>Level  | -100             | mV |                                      |

| Maximum Programmable Logic Low<br>Level  | 600              | mV |                                      |

| Logic Level Control Resolution           | 1                | mV |                                      |

| Logic Level Accuracy                     | Larger of 5.0 mV |    |                                      |

|                                          | or 2.0 % of      |    |                                      |

|                                          | programmed       |    |                                      |

|                                          | value            |    |                                      |

Table 7 Clocking Characteristics

| Parameter                                       | Value | Units | Description and Conditions |

|-------------------------------------------------|-------|-------|----------------------------|

| Internal Time Base                              |       |       |                            |

| Number of Internal Frequency<br>References      | 1     |       |                            |

| Frequency Resolution of<br>Programmed Data Rate | 1     | Kbps  |                            |

Table 8 Pattern Handling Characteristics

| Parameter                        | Value           | Units | Description and Conditions |

|----------------------------------|-----------------|-------|----------------------------|

| Preset Patterns                  |                 |       |                            |

| Standard Built-In Patterns       | PRBS.5          |       |                            |

|                                  | PRBS.7          |       |                            |

|                                  | PRBS.9          |       |                            |

|                                  | PRBS.11         |       |                            |

|                                  | PRBS.13         |       |                            |

|                                  | PRBS.15         |       |                            |

|                                  | PRBS.18         |       |                            |

|                                  | PRBS.23         |       |                            |

|                                  | PRBS.31         |       |                            |

| Pattern Choice per Transmit      | Per-transmitter |       |                            |

| Channel                          |                 |       |                            |

|                                  |                 |       |                            |

|                                  |                 |       |                            |

| User-programmable Pattern Memory |                 |       |                            |

| Individual Force Pattern         | Per-transmitter |       |                            |

| Minimum Pattern Segment Size     | 16              | bits  |                            |

| Maximum Pattern Segment Size     | 4G              | Bytes |                            |

| Maximum Number of Unique         | 128             |       |                            |

| Pattern Segments                 |                 |       |                            |

| Total Memory Space for           | 4G              | Bytes |                            |

| Transmitters                     |                 |       |                            |

| Pattern Sequencing                 |                     |                                                           |

|------------------------------------|---------------------|-----------------------------------------------------------|

| Sequence Control                   | Loop infinite       |                                                           |

|                                    | Loop on count       | Count is a number that is specified later in this section |

|                                    | Play to end         |                                                           |

| Number of Sequencer Slots per      | 16                  | Each pattern generator can string up to 16 different      |

| Pattern Generator                  |                     | segments together, each with its own repeat count.        |

| Number of Entry Slots              | 1                   | Separate from above 16 segments.                          |

| Number of Exit Slots               | 1                   | Separate from above 16 segments and entry slot.           |

| Maximum Loop Count per             | 2 <sup>16</sup> - 1 |                                                           |

| Sequencer Slot                     |                     |                                                           |

|                                    |                     |                                                           |

|                                    |                     |                                                           |

|                                    |                     |                                                           |

| Additional Pattern Characteristics |                     |                                                           |

| C-PHY Encoder & Mapper             | Per Lane            |                                                           |

| Escape Mode Command Entry          | Per Lane            |                                                           |

| Pattern Switching                  | Wait to end of      | When sourcing PRBS patterns, this option does not         |

|                                    | segment             | exist.                                                    |

|                                    | Immediate           |                                                           |

| Revision Number | History                             | Date              |

|-----------------|-------------------------------------|-------------------|

| 1.0             | Import from internal documentation  | November 1, 2014  |

| 1.1             | Formatting and typesetting          | November 18, 2014 |

| 1.2             | Updated figure 2, maximum data rate | November 20, 2014 |

| 1.3             | Updated document template           | June 10, 2015     |

The information in this document is subject to change without notice and should not be construed as a commitment by Introspect Technology. While reasonable precautions have been taken, Introspect Technology assumes no responsibility for any errors that may appear in this document.